Annual III Research Report 2013 0

0

Multi-Cole

Architecture and IC Design, Embedded Software

0

100001101

frequ

\magers

0

Parallel S

17150

$\bigcirc$

Leti is an institute of CEA, a French research-and-technology organization with activities in energy, IT, healthcare, defense and security. By creating innovation and transferring it to industry, Leti is the bridge between basic research and production of micro- and nanotechnologies that improve the

Leti partners with large industrials, SMEs and startups to tailor advanced solutions that strengthen their competitive positions. It has launched more than 50 startups. Its 8,000m<sup>2</sup> of cleanroom space feature 200mm and 300mm wafer processing of micro and nano solutions for applications ranging from space to smart devices. Leti's staff of more than 1,700 includes 200 assignees from partner companies. Leti is based in Grenoble, France, and has offices in Silicon Valley, Calif., and Tokyo.

#### Visit www.leti.fr for more information

lives of people around the world.

**List,** an institute of **CEA**, is a key player in Information and Communication Technologies. Its research activities are focused on Digital Systems with major societal and economic stakes: Embedded Systems, Ambient Intelligence and Information Processing. With its 650 researchers, engineers and technicians, the CEA-LIST performs innovative research in partnership with major industrial players in the fields of ICT, Energy, Transport, Security & Defense, Medical and Industrial Process. List is based in the Paris-Saclay campus, France.

Visit www-list.cea.fr for more information

**Design, Architectures & Embedded Software** research activity is shared between Leti and List through a dedicated division. More than 280 people are focusing on RF, digital and SoC, imaging circuits, design environment and embedded software. These researchers perform work for both internal clients and outside customers, ranging from startups and SMEs to large international companies.

| Editorial<br>Thierry Collette, Head of Architecture &<br>IC design, Embedded Software Division | 5  |

|------------------------------------------------------------------------------------------------|----|

| Key Figures                                                                                    | 7  |

| Scientific Activities                                                                          | 9  |

| Smart Interconnected Devices                                                                   | 11 |

| Digital Architectures & Systems                                                                | 43 |

| Power & Temperature Optimized<br>Digital Circuits                                              | 75 |

| Circuits in Emerging Technologies                                                              | 89 |

| PhD Degrees Awarded                                                                            | 95 |

•

More than ever, considering the wave of the Internet of Things / Cloud of Things, the constraints of software / hardware integration within integrated and embedded systems are a priority. Indeed, the IoT, as an extension of the embedded systems domain, is a major and wide issue, that addresses the devices, servers and services.

For these three areas, system and component integration is the key, involving major challenges as ultra-low power (in sensors and actuators, communications, computing from smart devices to servers, and energy harvesting, conversion and management), easy and scalable deployment, reliability, dependability, security and privacy in these new fully connected infrastructure.

All these issues are driving our current research activities, aiming to provide tomorrow innovative solutions to our industrial partners. These topics are addressed in this report with sections dedicated to Smart Interconnected Devices, Digital Architectures & Systems, Power & Temperature Optimized Digital Circuits, and Circuits in Emerging Technologies.

We hope you will appreciate reading this report that gives you an overview of our latest research.

Thierry Collette

# Annual Research Report 2013 . . Leti List

Architecture and IC Design, Embedded Software

# **Key Figures**

2 locations: MINATEC Campus (Grenoble) PARIS-SACLAY Campus (Palaiseau)

**174 Permanent researchers, 65 PhDs and Post-docs**

Design & Embedded system plateform Full suite of IC CAD and Embedded system tools, Hardware Emulators, & Test equipments,

34M€ budget 85% funding from contracts

46 granted patents 38 papers, journals & books 175 conferences & workshops

# Annual Research Report 2013 🔹 Leti Li/t

Architecture and IC Design, Embedded Software

# **Scientific Activity**

#### **Publications**

175 publications in 2013, including journals and Top conferences like ISSCC, VLSI Circuits Symposium, ESSCIRC, CICC, IMS, ISCAS, DAC, DATE, ACC, ECC, RTSS, IPDPS and ESWeek

#### **Distinctions and Awards**

Catrene Innovation Award – Panama project Nanoelectronic Forum 2013 Exhibition Awards: 2<sup>nd</sup> place SEEL project IEEE 3PGCIC'13 - Best Paper Award – Oana Stan 4<sup>th</sup> European Workshop on CMOS variability – Best Student Paper Award – Lionel Vincent RTNS 2013 – Best Student Paper Award – Vincent Legout

#### **Expertises and Recognitions**

41 CEA experts: 4 Research Directors, 2 International Experts9 Researchers with habilitation qualification (to independently supervise doctoral candidates)2 IEEE Senior Members

#### **Scientific Committees**

Editorial Boards: IEEE TCAS I, Journal of Low Power Electronics,

19 members of Technical Programs and Steering Committees in major conferences: ISSCC, ESSCIRC, DAC, DATE, ASP-DAC, ESWEEK, RTNS, IJCNN, IWANN, EMSOFT, NANOARCH...

Normalization committee: AUTOSAR (Automotive Open System Architecture)

#### **International Collaborations**

Collaborations with more than 20 universities and institutes worldwide Caltech, University of Berkeley, University of Columbia, Carnegie Mellon University, EPFL, CSEM, UCL, Polito Torino, KIT, Chalmers University, Tongji, ....

Imagers, Image Processors Sensor Interfaces Energy conversion RF communications Localization Middleware for IoT Diagnostic

# Smart Interconnected Devices

# A novel 0.5GHz real time single-photon detection technique: circuit design for cooled HgCdTe infrared APD detector

#### Research topics : Single-photon detection, photon counting, infrared sensor

H. Amhaz, K. Foubert , F. Guellec, and J. Rothman

ABSTRACT: A readout IC dedicated to mono-element photon detection in the SWIR infrared band has been developed. Its multi-channel architecture enables high detection rate. Each channel is hybridized to a HgCdTe avalanche photodiode (APD) that provides gain with low excess-noise. The input-referred channel noise is 12 electrons allowing single-photon detection with a APD gain (M) in the 30 to 50 range. For M=50, the detection efficiency reaches 98% with a 5ns p-p precision in the detection when taking into account the channel-to-channel mismatch. The channel detection rate is about 32MHz leading to a global rate above 0.5GHz.

The HgCdTe Avalanche Photodiode (APD) technology initially developed at CEA-Léti for infrared imaging application is also interesting for several mono-element applications due to the high gain, high bandwidth and low excess noise characteristics of this device.

Atmospheric and telemetric LIDAR applications require a high bandwidth (20MHz to 100MHz) and high sensitivity. Free-space telecommunication will require higher bandwidth (100MHz to several GHz). Other applications like spectrometry and photoluminescence require a very high sensitivity in order to detect a single photon.

In this context, we developed a versatile circuit that could satisfy various needs [1]. The main applications require a minimum photosensitive area of  $100 \times 100 \mu m^2$ . From a technological point of view it is difficult to make large APD with good performances. Consequently, a 5x5 diode array has been used to cover the surface based on a 25µm pitch.

The read-out IC (ROIC) specifications needed to cover a large panel of applications are quite demanding. In addition to real-time single-photon detection the mono-element detector should be available to work over a high input photon rate range.

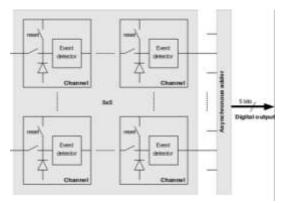

A multi-channel approach has been adopted in order to increase the global detection rate (Fig. 1). Each APD is connected to an event detector and the digital outputs of the channels are added to provide a 5-bit asynchronous data representing the events detected over the whole area.

Figure 1: Multi-channel detector architecture

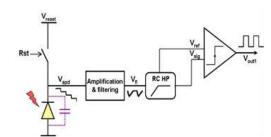

The input current is directly integrated on the photodiode junction capacitance producing a staircase signal with small steps ( $250\mu V$  per photon for an APD gain M=30). This signal is amplified and filtering is then applied to use a detection scheme based on transition rather than level (Fig. 2).

Figure 2: Bloc diagram of the event detection circuit

The simulated input-referred temporal noise is about 12 electrons. This performance allows single-photon detection with low false count rate (10e-3 to 10e-5) at moderate APD gain (30 to 50). The event detection circuit works asynchronously and is able to distinguish 2 photons separated by 31ns. Thanks to the detector's asynchronous multi-channel architecture, the 32MHz channel rate lead to a global photon detection rate above 0.5GHz when considering uniform illumination over a 100x100µm<sup>2</sup> area (4x4 channels with 25µm pitch).

In the chosen architecture, channel-to-channel mismatch is also a key issue that may limit the temporal precision of the detection. The circuit has been designed to have a low sensibility to amplifier and comparator offsets. As a result the channel-to-channel delay variation is around 5ns p-p. Mismatch also affects Photon Detection Efficiency (PDE). Monte-Carlo simulations have shown that a PDE of 98% is obtained for an APD gain of 50. While it is not possible to perform single-photon detection with M<20, the PDE is still rather good at 85% for M=30.

The circuit has been fabricated in a standard  $0.18\mu$ m 1.8V/3.3V CMOS process. The goal is to demonstrate the advantage of this detector technology by implementing the prototype in different experimental setups covering several applications.

Related Publications :

[1] H Amhaz, K. Foubert, F. Guellec, et al., "A Novel 0.5GHz Real Time Asynchronous Photon Detection and Counting Technique: ROIC Design for Cooled SWIR HgCdTe Infrared Detector", IEEE International NEWCAS conference, 2013.

# A [10°C ; 70°C] 640×480 17µm Pixel Pitch TEC-Less IR Bolometer Imager with Below 50mK and Below 4V Power Supply

#### **Research topics : Thermo Electrical Cooler Less, Infra Red, Imager, Bolometer**

B. Dupont, A. Dupret, S. Becker, A. Hamelin, F. Guellec, P. Imperinetti, W. Rabaud

ABSTRACT: Used in low cost thermal imaging, infrared micro-bolometer detectors are very demanding in terms of offset skimming and technological fluctuation compensation. To reach a noise equivalent temperature difference (NETD) about 50mk, and considering the dependence of both offset and Fixed-Pattern Noise (FPN) on the temperature of the focal plane, a thermo electrical cooler (TEC) is used to prevent the temperature of the focal plane from varying either spatially or temporally. This paper presents an architecture that allows to get rid off the TEC, while keeping performances at the state of art.

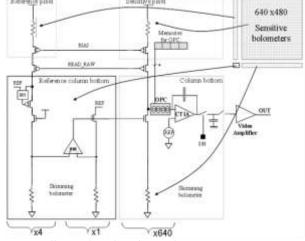

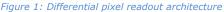

This circuit is based on an enhanced differential pixel read out (Fig.1.). As all micro-bolometer imagers, this circuit is based on sensitive thermistor arrays. Bolometer resistance varies according to its temperature, which is linked to biasing, self-heating, focal plane temperature and scene temperature. The difference between the sensitive bolometers and a reference bolometer gives an image of the scene temperature. This difference is less accurate when the characteristics of the reference bolometer differ from the sensitive bolometer (polarization, duty cycle and physical design). The read out circuit also impacts the accuracy of the difference and its sensitivity to temperature. To sum-up the TEC-less characteristic implies to keep output NETD over a large thermal range without tuning supplies or polarizations of the circuit. So it depends on conversion gain, mismatch and offsets level drift.

In the presented circuit, the reference is provided by a column of shielded bolometer with the same characteristics as the sensing bolometer and located at the head of rows of the pixel array. Since the pixel array is read in a rolling shutter way, the shielded bolometer has the same thermal cycle as the sensing bolometers. For both the reference and the sensing branch, PMOS voltage followers with identical gate voltage force identical voltage across both bolometers.

A Buffered Direct Injection (BDI) forces Vref on the drain of the PMOS of the reference branch. It prevents Early effect and allows a more accurate copy of the current. To keep the reference branch noise below that of the sensing branch, dominated by 1/f noise, large NMOS are designed. As a result the BDI load about 800pF, and rejects the 1/f noise by a factor of 50 in the [1Hz ; 5KHz] bandwidth.

Regarding the transimpedance amplifier (CTIA), its gain can be set between 5 and 70V/ $\mu$ A. At 30°C such a high gain allows having an output NETD only 2% higher than the intrinsic sensing bolometer NETD.

To compensate the remaining FPN, an offset pre-correction (OPC) is implemented: thermalized bolometers provide currents {Ioff, Ioff/2, Ioff/4, Ioff/8} that are combined according to the 4-bit values stored in each pixel. By reducing mismatch impact before integration OPC prevents the CTIA from saturating under thermal drift, especially at high gain. By being less sensitive to thermal drift, a low gain would enable a larger TEC less range but the read out chain would intolerably degrade the output NETD.

Conversely for a given TEC-less range, the OPC enables reducing the constraints on bolometer mismatches. This constitutes a key factor when low-cost micro-bolometer imagers are targeted.

The readout chain accounts for about 95% of the 170mW total power consumption.

Designed in 0.18 $\mu$ m CMOS technology presented ROIC allows a TEC-less capability with a low 4V power supply without using off-chip compensation tables. To the best of our knowledge, this micro-bolometer imager is the only 17 $\mu$ m pixel pitch that features a NETD less than 50mK over a [10°C; 70°C] operating range.

The differential architecture is naturally TEC-less whatever the bolometer resistance values are.

The digital OPC reduces the impact of FPN and contribute to extend TEC-less range. Finally the enhanced differential architecture also rejects supply noise by a factor of 50, making this circuit fully compliant with harsh environment.

Related Publications :

[1] Bertrand Dupont, Antoine Dupret, Sebastien Becker, Antoine Hamelin, Fabrice Guellec, Pierre Imperinetti, Wilfried Rabaud: A [10°C; 70°C] 640×480 17µm pixel pitch TEC-less IR bolometer imager with below 50mK and below 4V power supply. ISSCC 2013: 394-395

# A 120µW 240×110@25fps vision chip with ROI detection SIMD processing unit

#### Research topics : CMOS image sensors, low power, analog processing

A. Verdant, A. Dupret, P. Villard, L. Alacoque, H. Mathias (IEF), F. Delgehier (IEF)

ABSTRACT: A smart ultra-low power CMOS image sensor comprising an analog programmable processor array is reported. Compact and efficient motion detection algorithms are implemented to process sub-sampled images made of so-called macropixels. Only Regions of Interest (ROI) consisting of macropixels containing moving objects are read out. This drastically reduces power consumption: the 110×240 pixel image sensor fabricated in a 0.35µm technology features a power consumption of 120µW at 25fps.

Achieving ultra-low power consumption is of most importance for battery powered image sensors. In the case of video surveillance applications, this power consumption can be adapted to the scene activity. However, the detection of intrusions implemented on processors associated to video cameras wastes a considerable amount of power. Indeed, every frame of the whole image array is processed, whereas the actual scene is steady, or merely comprises very few and small regions of interest (ROIs).

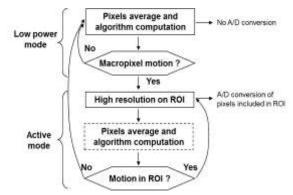

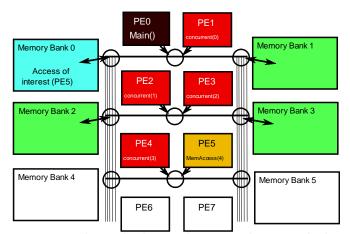

A CMOS image sensor capable of efficiently detecting and tracking ROIs with ultra-low power consumption has been designed. The circuit has been optimized to implement various motion detection algorithms, from which derives the locations of ROIs. Those algorithms based on the difference between the actual scene and an estimate of its background, obtained from the temporal filtering of the macropixels' luminance, are among the most compact ones [1]. The image sensor proof of concept is composed of a 240×110 pixel array associated to a Single Instruction Multiple Data (SIMD) vector of 11 general purpose analog programmable processing units (PUs) and to 5 banks of  $24 \times 11$  analog memory array (ARAM) (Figure 1).

Figure 1 : Global ASIC architecture

The computations are performed on the local average of  $10 \times 10$  pixels. These averages are acquired in rolling shutter mode, as well as full resolution sub-images (ROIs).

By using this sub-sampling scheme, the data throughput towards the processing elements is divided by 100, while keeping the contribution of all the pixels.

The results of the computations are used to detect critical temporal activity, considered as moving objects, and to give the location of the regions of interest (ROIs) where moving objects have been located. Only the pixels within the macropixels elected as ROIs are driven outside the sensor by a readout pipeline opposite to the vector of PUs. As long as no motion appears, the high resolution pixels are not read out, which contributes to further reduce the power consumption. The general sensor behavior is exposed on Figure 2.

Figure 2 : Synoptic describing sensor behavior for motion detection processing and high resolution pixel readout

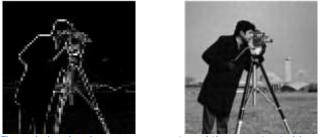

Various compact motion detection algorithms have been implemented, achieving Detection Rate as high as 95%. An image acquired with the presented sensor is exposed on Figure 3.

Figure 3 : Example of ROI detection

The total power consumption of the pixel array, PUs and memory is  $120\mu W$ . Using standard batteries of about 1 A.h, the autonomy of the presented sensor reaches one year.

Related Publications :

[1] Arnaud Verdant, Patrick Villard, Antoine Dupret, and Hervé Mathias, "Three Novell Analog-Domain Algorithms for Motion Detection in Video Surveillance," EURASIP Journal on Image and Video Processing, vol. 2011, Article ID 698914, 13 pages, 2011. doi:10.1155/2011/698914.

[2] Arnaud Verdant, Antoine Dupret, Patrick Villard, Laurent Alacoque, Hervé Mathias, and Flavien Delgehier, "A 120µW 240×110@25fps vision chip with ROI detection SIMD processing unit", ISCAS, page 2412-2415. IEEE, (2013)

# 3D integrated burst CMOS image sensor for high speed applications

#### **Research topics: High Speed Imaging, Burst Image Sensor, 3D Integration**

R. Bonnard, F. Guellec, J. Segura, A. Dupret, W. Uhring (ICube)

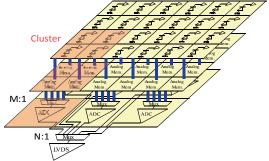

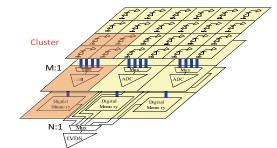

ABSTRACT: As 3D integration appears to be a key enabling technology for future image sensors, it is especially true for high speed imaging. We present two new 3D stacked architectures for burst high speed imaging with in-situ A/D conversion, one with analog memories, the other based on digital storage. Thanks to our research, analog storage architecture appears as a good way to reach unmatched speed performances (>10 Terapixel/s) while digital storage architecture seems an interesting solution to reach high memory depth (>200 frames).

High speed imaging is a cutting edge technology useful in many technical and scientific fields as a measuring instrument and a monitoring tool. These sensors are used to study fast phenomena like fracture mechanics, fluorescence life time, plasma forming, etc. Two kinds of high speed image sensor (IS) must be distinguished: continuous IS and burst IS. In continuous mode, the image sensor acquires and reads out of the chip the frames one after the other. However due to the limited number of output channels, the readout circuits are the bottlenecks which limit the frame rate to tens of kilo-frames-per-second (fps). To overcome this limit, a solution is to acquire at higher rates and store a burst of frames on chip before read out. 3D integration appears to be a key technology to design burst image sensor. Indeed it allows to perform highly parallel acquisition and to store a large number of frames while keeping a good pixel fill factor (i.e. good sensitivity).

We propose two architectures of burst image sensor with on-chip A/D conversion, one with analog storage, Fig. 1 and one with digital storage, Fig. 2. For the analog storage architecture, the front end electronic captures (1st tier) and stores (2nd tier) the burst in an analog memory. Then, the ADCs convert (3rd tier) the frames into digital data which are serialized read out through the output driver (3rd tier).

Figure 1: Burst image sensor with analog storage architecture

In digital storage architecture the A/D conversion is performed before the frame storage as shown. First, the pixel signals (1st tier) are converted into digital signals (2nd tier) which are stored into digital memories (3rd tier). Then, the digital memory is read out of the pixel through an output driver (3rd tier).

Figure 2: Burst image sensor with digital storage architecture

In [1] we propose appraisals of frame-rate, memory depth and power consumption for both architectures which are summarized in Fig. 3.

| Storage | Pixel<br>Size<br>(µm) | Resolution<br>(pixel) | Frame<br>Rate<br>(Mfps) | Memory<br>Depth<br>(frame) | Power<br>(W) |

|---------|-----------------------|-----------------------|-------------------------|----------------------------|--------------|

| Analog  | 40x40                 | 500x500               | 100-<br>1000            | ~80                        | 2            |

| Digital | 40x40                 | 500x500               | 1-10                    | >200                       | 11           |

Figure 3: Performance assessment

The architecture analysis shows that digital storage architecture has a slower frame rate (up to 10 mega-fps) than analog storage architecture but has a higher memory depth which can easily exceed 200 frames for a 40µm pixel pitch. In terms of power consumption, the analog storage architecture is more energy efficient than the digital one. Moreover during the burst acquisition, the power consumption of both architectures skyrockets due to memory accesses. Compared to the state of the art (SOA), on one hand, 3D analog storage architecture would allow 100 to 1000 mega-fps while SOA reaches 10-20 mega-fps for 2D image sensor with about the same memory depth. On the other hand, 3D digital storage architecture allows to store more than 200 frames per burst while present burst image sensors do not exceed 150 frames.

Related publication: [1] Bonnard, R.; Guellec, F.; Segura, J.; Dupret, A.; Uhring, W., "New 3D-integrated burst image sensor architectures with in-situ A/D conversion," 2013 Conference on Design and Architectures for Signal and Image Processing (DASIP), vol., no., pp.215-222, 8-10 Oct. 2013

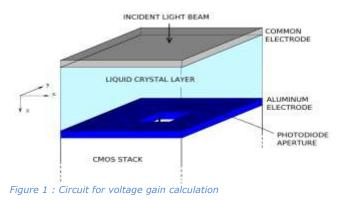

# Co-integration of a Smart CMOS Image Sensor and a Spatial Light Modulator for Real-Time Optical Phase Modulation

#### Research topics: CMOS Image Sensor, Optical phase modulation, Acousto-optic

T.Laforest, A.Verdant, A. Dupret, S. Gigan\*, F. Ramaz\*, G. Tessier\* (\*ESPCI ParisTech)

ABSTRACT: we present a CMOS image sensor architecture coupling a spatial light modulator to a special scheme photodiode, for medical imaging based on acousto-optical coherence tomography with a digital holographic detection. Our architecture is able to measure an interference pattern between a scattered beam transmitted through a scattering media and a reference beam, on an array with 16 µm pixel pitch, at 4000 Hz. This is compliant with correlation time of breast tissues. The stacking of a photosensitive element with a spatial light modulator on the same device brings a significantly higher robustness compared to the state of the art techniques.

Optical imaging through biological media is strongly limited because of light scattering. This is especially problematic in medical imaging, when the goal is to detect a millimetersized object within a several centimeters thick scattering medium, e.g. for early breast cancer detection. The resolution of a breast tissue image obtained from diffuse optical tomography is usually around 10 mm. As a result, emerging tumors cannot be detected. The use of an acousto-optical holographic scheme allows obtaining a 10 fold improvement resolution [2]. Indeed, such a technique enables foreseeing great progress in breast medical imaging in the near future.

However, its clinical application is still out of reach because of the complexity of the setup and the limitations of the detection scheme. One of the major problems is that in thick biological tissues, the correlation time of the transmitted intensity through the sample is typically a few milliseconds. Furthermore, the relevant signal (i.e. useful to extract optical information) corresponds to 10% of the total incident light power on the sensor. As a consequence the detector must have at the same time a frame rate higher than 2 kfps and a noise level compliant with the detection of the scattered beam.

Moreover, coupling acousto-optic holographic scheme with a spatial phase modulation setup allows phase conjugation

and light focusing through the sample on a region of interest. This focusing would make detection much easier, e.g. by improving the acousto-optic signal coming from the region of interest. State of the art setups are based on the association of a camera, which acts as a wavefront sensor, and a spatial light modulator. The camera sends the measured phase of the wavefront to a processing unit, which in turn sends a feedback control to the modulator for phase-conjugation and focusing of light on the regions of interest. Such a principle has been recently investigated using different techniques and shows a great interest not only for imaging diagnosis but also for therapy in thick biological media. Nevertheless, the phase conjugation setup presents several limitations. Firstly, the modulator and the camera pixel arrays must be perfectly matched spatially but this is at the cost of complicated mechanical processes, both bulky, complicated to align and expensive. Secondly, separated elements lead to a feedback delay that prohibits controlling light, corresponding typically to some hundreds of milliseconds, which is incompatible with the analysis of living tissues.

In order to address these limitations, we propose an architecture for a CMOS image sensor that is dedicated to wavefront acquisition and modulation. The pixel integrates a photodiode with some analog primitives and a spatial light modulator (SLM) made of liquid crystal covering the entire pixel. This stacking, shown in Fig 1, allows a perfect matching between photodiode and SLM pixels. The pixel to SLM connectivity circumvents the latency due to rolling mode readout. As a consequence this stack allows a delay free feedback between photodiode data to SLM control, making the image sensor compliant with biological media correlation time constrains.

An architecture for an original pixel coupling a spatial light modulator and an image sensor has been presented in [1,2]. Optical simulations have also been presented in [3].

[2] Laforest, T.; Dupret, A.; Verdant, A.; Ramaz, F.; Gigan, S.; Tessier, G "Co-Integration of a Smart CMOS Image Sensor and a Spatial Light Modulator for Real-Time Optical Phase Modulation.", SPIE Electronic Imaging 2014.

[3] Laforest, T.; Dupret, A.; Verdant, A.; Ramaz, F.; Gigan, S.; Tessier, G, "Monolithic device for on-chip fast Optical Phase Conjugation

integrating an image sensor and a spatial light modulator", SPIE Photonics West 2014.

**Related Publications:**

<sup>[1]</sup> Laforest, T.; Dupret, A.; Verdant, A.; Ramaz, F.; Gigan, S.; Tessier, G.; Benoit a la Guillaume, E., "A 4000 Hz CMOS image sensor with in-pixel processing for light measurement and modulation," New Circuits and Systems Conference (NEWCAS), 2013 IEEE 11th

## New applications and sensing strategies for compressive sensing

#### **Research topics: High Dynamic Range, Compressive Sensing, Features extraction**

W.Guicquero, A.Dupret, P.Vandergheynst (EPFL)

ABSTRACT: With the rise of compressive sensing image sensors, it becomes necessary to define relevant sensing schemes and applications. Our work aims at proposing new applications and sensing strategies for that purpose. Since new sensing schemes become practical on real image sensors, side applications will emerge. In this work, we have proposed two novel applications, Compressive Feature Imaging [1] and High Dynamic range Compressive Sensing [2].

The motivation of this work is to generalize the Compressive Sensing (CS) paradigm to novel applications and sensing methods. First we propose a nonlinear sensing strategy providing relevant features [1] for classification purpose -for example- and secondly a High Dynamic Range CS multicapture method [2].

We demonstrate in [1] that block variance is a good candidate for tuning the number of measurements performed by block in the context of adaptive block-based CS. It is also shown that block variances can be used as nonlinear CS measurements. In addition, such a statistical descriptor could easily be implemented in the analog domain before the analog to digital conversion into an image sensor. Those features can also be used as features for tracking or classification purposes. The best reconstruction results shown in figure 1 are obtained using a proposed constraint operator on the image x. Op(x) is composed of multiple wavelet transforms (mWT) on horizontal and vertical gradients (TV).

$$Op(x) = \left\| mWT(TV(x)) \right\|_{1}$$

Eq.1

Figure 1: Local variance measurements and the reconstructed image (PSNR = 31.1 dB) with a compression ratio of 7.8%.

Multi-capture HDR implies to store full frame images. This technique is based on acquiring multiple images from a single scene using multiple different times of exposure. The goal is thus to acquire low illumination regions with a long time of exposure and respectively high illumination regions using a short time of exposure. This way, a HDR image can be reconstructed from those different images preserving low dynamic details in low illumination regions and eliminating saturation problems for highest illumination regions.

However, it requires either a lot of memory resources or digital processing power to perform compression. CS can reduce a lot those memory requirements at the sensor level. Assuming that a HDR image is sparse in some sense, the image can be reconstructed from relatively few measurements performed on images corresponding to different times of exposure. In the proposed method, a global tone-mapping (tm) has been added to make the reconstructed image of a better quality in terms of visual rendering. The proposed constraint operator on RGB image x is expressed in Eq.2. It is composed of multiple wavelet transforms (mWT) on the YUV color representation of the tone mapped version of x joint with the Total Variation (TV) of tm(x). Figure 2 shows an example of an HDR CS reconstruction.

#### $Op(x) = \|mWT(YUV(tm(x))) + TV(tm(x))\|_{1} \quad \text{Eq.2}$

Figure 2: Original16-bit image and its tone mapped reconstruction (PSNR = 42 dB) (demosaicing, dynamic range increasing of 18dB).

This work exposes a novel approach for multi-capture imaging taking advantage of the CS paradigm. The proposed technique performs at the same time a HDR reconstruction for the three color channels. It opens a new way to design compressive sensing image sensor particularly adapted to acquire HDR images. The dynamic range of the acquisition can be largely increased without imposing a huge amount of data comparing to a classical multi-capture. In addition, a new set of constraints is proposed for the color image reconstruction problem, referring to demosaicing. Those constraints are applied on different color spaces to jointly reconstruct color channels of the demosaiced HDR image.

Related Publications:

- [1] W. Guicquero, A. Dupret, P. Vandergheynst, "A adaptive compressing sensing with side information" (IEEE ASILOMAR CSS&C), 2013.

- [2]W. Guicquero, A. Dupret, P. Vandergheynst, "Multi-capture high dynamic range compressive imaging" (IEEE ASILOMAR CSS&C), 2013.

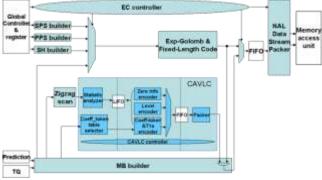

# Hardware Implementation for Entropy Coding and Byte Stream Packing Engine in H.264/AVC

#### Research topics : H.264/AVC, entropy coding, CAVLC, Exp-Golomb, Video byte stream

N-M. Nguyen, E. Beigne, S. Lesecq, P. Vivet, D-H. Bui (VNU), X-T. Tran (VNU)

ABSTRACT: Entropy coding (EC) and data packing are the major phases in video coding. The H.264 Advanced Video Coding (H.264/AVC) standard adopts Exp-Golomb and Context-Adaptive coding methods to increase data compression ratio. We propose a hardware architecture of EC and byte stream data packing engines for the H.264/AVC. Our EC engine, containing Exp-Golomb and Context-Adaptive Variable Length Coding (CAVLC), supports the baseline and main profiles of the standard. The proposed architecture is implemented using 180nm technology from AMS. The design consumes only 1.56mW at the operating frequency of 100MHz.

Recommended by both the ITU-T Video Coding Experts Group (VCEG) and the ISO/IEC Moving Picture Experts Group (MPEG), the H.264 Advanced Video Coding (H.264/AVC) can save approximately 50% of bit rate in comparison with previous standards **Erreur ! Source du renvoi introuvable.**thanks to the adoption of several features. The H.264/AVC also provides high loss/error robustness using separated parameter set structures, which keep key information. For instance, the NAL unit syntax structure enables "network friendliness" to customize the use of the Video Coded Layer (VCL) for various systems and networks.

Many works propose hardware (HW) implementation of the standard. However, they mostly focused on the prediction part of encoders/decoders and on the improvements of algorithms. It can be seen in the literature that for EC in baseline profile (i.e. the Exp-Golomb and CAVLC coding techniques), hardware EC engines usually only encode the data at MB level, i.e. SPS, PPS and Slice header might be implemented in software.

*Figure 1: Architecture of entropy coder.*

We propose a new architecture of the entropy coding and data packing engine as shown in Figure 1. Encoded syntax elements are transferred from entropy coding to data packing via a FIFO. The main part of the entropy coding engine consists of two encoders, namely, the Exp-Golomb and Fixed-length code (EGF) and CAVLC modules [1]. SPS, PPS, SH, and MB builders are implemented to collect the tobe-encoded data and send them to the EGF module in the specified order. SPS, PPS, SH's information is provided by a global controller via system registers. The MB header information is received from Intra-, Inter- and TQ engines.

The architecture proposed has been modeled in VHDL at RTL level. To verify, our EC and data packing module has been integrated into a hardware H.264 video encoding system. Using the video encoder system with the proposed EC NAL module, we encode raw test video sequences in the CIF format (which is one format we target as it is used for mobile applications). The encoded videos are received from the output of the data packing module. For validation purpose, these encoded videos are then successfully decoded with the JM decoder.

The simulation is done by using ModelSim from Mentor Graphics and the design is synthesized with AMS CMOS 180nm technology by using DC Compiler from Synopsys. Some implementation results of our EC and byte-stream packing data engines are presented in Table 1.

| Table 1: Implementation results of the proposed design |            |           |              |           |  |  |  |  |

|--------------------------------------------------------|------------|-----------|--------------|-----------|--|--|--|--|

| Technology                                             | Cycles/MB  | Frequency | Area<br>cost | Power     |  |  |  |  |

| AMS                                                    | 691 in the | 100MHz    | 73.5         | 1.56mW    |  |  |  |  |

| 0.18µm                                                 | worst case |           | Kgates       | at 100MHz |  |  |  |  |

Due to the implementation of the table selector for coeff\_token syntax element and the full hardware implementation of the EC, including SPS, PPS, slice header data generators, our design occupies a slightly larger silicon area (approximately 73.5Kgates) than the ones found in the literature.

However, in terms of throughput, our EC engine encodes an MB in maximum 691 cycles (151 cycles for the worst case of MB header plus 540 cycles for the worst case of residual data). With this speed and at the operating frequency of 100MHz, the design is suitable for 720HD video format. Moreover, in average, the encoding process only requires 25 to 90 cycles for MB header and 450 cycles for MB residual.

In terms of power consumption, at 100MHz, it only consumes 1.56mW which is less than most of the low-power designs that operate at 27MHz.

More information on our design can be found in [2].

**Related Publications:**

[1] N.-M. Nguyen, X.-T. Tran, P. Vivet, and S. Lesecq. An efficient Context Adaptive Variable Length coding architecture for H.264/AVC video encoders. International Conference on Advanced Technologies for Communications (ATC), pp. 158–164, 2012.

[2] N.-M. Nguyen, E. Beigne, S. Lesecq, P. Vivet, D.-H. Bui, X.-T. Tran, Hardware implementation for entropy coding and byte stream packing engine in H.264/AVC, International Conference on Advanced Technologies for Communications (ATC), pp. 360-365, 2013.

# **GESTURE RECOGNITION ON SMART CAMERAS**

#### **Research topics: Gesture Recognition algorithms, embedded systems, Smart camera.**

A. Dziri, S. Chevobbe, M. Darouich

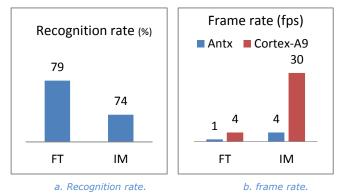

ABSTRACT: Gesture recognition allows a natural interaction without using complex devices. However, most real-time methods are designed to work on computers with high computing resources and memory. This work aims to analyze the relevant methods and investigates the ability of hand gesture recognition on smart camera. Indeed, two gesture pipelines are designed and implemented on embedded processors. The results obtained show that gesture recognition with an acceptable recognition rate (70-80%) can be executed in real-time (4-30 fps) and uses about 200 kB of memory on embedded processors that can be used in smart cameras.

Several gesture recognition methods are developed to allow a natural human-machine interaction. However, these methods are designed without considering the computing resources and the amount of memory available in the embedded systems used in smart cameras. Furthermore, recognition systems use sophisticated sensors like Kinect, Time-of-Flight camera or stereo cameras. Theses sensors are more expensive and less compact than a smart camera. Smart camera is a compact vision system integrating an image sensor, low power embedded processors and low capacity memory on the same chip. This work consists in investigating the gesture recognition for ultra-integrated smart cameras. Gesture recognition on smart camera is a challenging problem because of the low computing resources available: low clock frequency for the processor, no floating point unit (FPU) and a small amount of memory (<1 MB).

To meet the challenge, we proposed two gesture recognition pipelines. Each pipeline is composed of two main blocks as shown in the Fig.1. In the first pipeline, the gesture recognition method is based on the use of invariant moments. The second one is based on finger tips detection. Both pipelines are implemented to comply with the constraints of embedded processors that we find in smart cameras. Indeed, floating-point to fixed-point conversion was performed and memory usage reduced. After, we analyzed for each pipeline its performances (recognition rate, frame rate and memory) on embedded processors.

In this study we targeted two embedded processors Antx [2] and ARM Cortex-A9. Antx is a simple low footprint processor that integrates neither hardware multiplier nor FPU. This processor is close to the embedded processors that we find in the ultra-integrated smart cameras. In the other hand, Cortex-A9 is powerful embedded processor that can be used for high performance smart cameras.

The results of performances analysis of both pipelines are shown in the Fig.2. The recognition rate is given by the Fig.2.a. and the execution time on the embedded processors is given by the frame rate in the Fig.2.b. The memory analysis from our implementation shows that less than 200 kB is required for each pipeline.

*Figure 2: Performances of finger tips and invariant moment pipelines: IM:invariant moments, FT: finger tips.*

The results obtained show that the gesture recognition can be executed on embedded processors for few gestures in real-time with an acceptable recognition rate. Future works will consist in implementing the pipeline of finger tips detection on the real smart camera to perform humanmachine interaction. Another possible study would be to modify the pipeline to improve the recognition rate.

Related Publications:

A. Dziri, S. Chevobbe, M. Darouich, "Gesture recognition on smart cameras", Proceeding of SPIE 2013, 86590L-86590L-15

C. Bechara, A. Berhault, N. Ventroux, S. Chevobbe, Y. Lhuillier, R. David, D. Etiemble, "A small footprint interleaved multithreaded processor for embedded systems", IEEE International Electronics Circuits and Sydstems (ICECS), 2011, pp. 685-690.

# Use of wavelet for image processing in smart cameras with low hardware resources

#### **Research topics : Wavelet, Demosaicing, Denoising, Recognition, Embedded systems**

S. Courroux, S. Chevobbe, M. Darouich, M. Paindavoine (LEAD)

ABSTRACT: In this work, we investigate the opportunity to use the wavelet representation to perform good quality image processing algorithms at a low computational complexity. Demosaicing, denoising, contrast correction and classification algorithms are executed over several well-known embedded cores (Leon3, Cortex A9 and DSP C6x). Wavelet-based image reconstruction shows higher image quality and lower computational complexity (3x) than usual spatial reconstruction. The use of wavelet decomposition also permits to increase the recognition rate of faces while decreasing computational complexity by a factor 25.

This work addresses the reconstruction and enhancement of a Colored Filter Array (CFA) image as well as the recognition of badly illuminated faces in the context of low resources cameras. Low and mid-quality processing chains have been designed and executed over different kind embedded processors such as control-oriented, general and DSP-like processors.

Wavelet-based processing chains outperform regular spatial algorithms both in terms of objective quality and computational complexity on low footprint general embedded processors as well as on DSP-like processors. However, in some special cases that have been highlighted, it is possible to process regular spatial-based processing chains faster but at lower quality than wavelet-based processing chains. Consequently, the use of the wavelet representation can help the designer to fit the requirements of the embedded domain.

Eigenfaces face classifier is used to achieve face recognition both in spatial and wavelet domains. In the latter case, only approximation coefficients are classified instead of the whole image. Unevenly face illumination highly degrades recognition rate. Consequently, a contrast correction algorithm is applied prior to the recognition task.

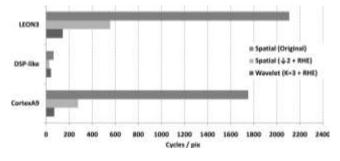

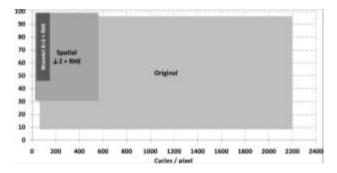

Figure 1: Computational complexity of the different recognition systems, executed over LEON3, Cortex A9 and the DSP-like processor

The computational complexity of three recognition processing chains: naïve, optimal spatial and optimal wavelet, are presented in Figure 1. The classification step requires one multiplication per cycle and per individual in the learning database. Executions on general purpose processors (LEON3 and CortexA9) show that wavelet-based method requires much less cycles than both naïve (15x) and optimal (4x) spatial processing pipelines. The same trends are observed for these two processors since spatial and wavelet processing chains require the same number of multiplication, an operator which is well optimized on the CortexA9. We observe that the length of the input vector has been reduced to 1.56 % of the original image size, while it is 100 % in the naïve case and 25 % in the optimal spatial case.

Figure 2: Quality versus computational complexity space of the face recognition application. Wavelet-based processing chain has high recognition rate and requires a low numbers of cycles, whatever the processor is.

Even with a larger vector size, spatial processing chains requires less cycles to execute on the DSP-like processor than wavelet processing chain. Concerning the two spatial chains, the compiler is able to provide a high instruction level parallelism (ILP), which increases performances. The ILP of the classification step is about 7.8 and 2.8 for RHE (Regional Histogram Equalization) algorithm. Consequently, when RHE and classification occupy respectively 9 and 91 %of the total execution time on LEON3, these operations represent respectively 40 and 60 % of the total execution time on CortexA9. As the ILP of the 2D DWT operation is about 1.6, wavelet-based recognition chains does not take advantage of the speedup due to the instruction-level parallelism of the DSP-like processor. The vector size reduction has a non-negligible impact on the memory footprint for the database storage. Indeed, for the optimal spatial case and naïve approach the memory needed is, respectively 600 KBytes and 2.5 MBytes, while it is only 40 KBytes for the wavelet case with 3 levels of decomposition (a reduction by a factor 15 to 64).

**Related Publications:**

<sup>[1]</sup> Courroux, S.; Chevobbe, S.; Darouich, M. & Paindavoine, M. (2013), 'Use of wavelet for image processing in smart cameras with low hardware resources ', Journal of Systems Architecture

# **128 nodes 4.5 mm pitch 15-bit Pressure Sensor Ribbon**

#### **Research topics : Aircraft metrology, high resolution pressure measurement, pressure**

C.Condemine, J.Willemin, S.Bouquet, S.Robinet, A.Robinet, L.Jouanet, G.Regis\*, S.Vitry\* (\*MIND)

ABSTRACT: Air-flow characterization for aircraft applications, demand high-density and high resolution pressure measurement. A ribbon of 128 15-bits thermally compensated pressure sensors was developed. Each sensor is compounded of off-the-shelf capacitive pressure transducer and an integrated specific sensor interface. The MEMS pressure sensor capacitance variations are converted into digital thanks to a second order switched caps sigma-delta converter. An innovative serial-bit sliding window FIR filter allows asynchronous data transfer. The global system noise is limited to 24 Pa in a range of [20kPa/95kPa] and [-30°C/+60°C].

To optimize a car or aircraft drag and pressure coefficients, both measurement and modeling are necessary. In parallel to mesh optimization in simulation tasks, in-situ advanced metrology must consequently be developed, using pressure monitoring, shape reconstruction, and MEMS sensor integration.

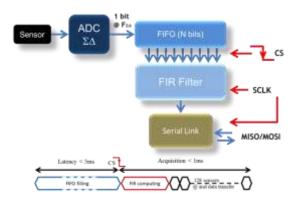

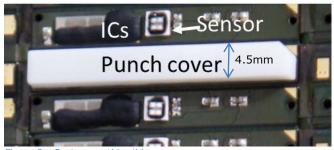

To that purpose, we developed a miniaturized air-flow sensing system to get high pressure measurement density (4.5mm pitch) on an aerodynamic shape [1]. In our specific application case, 128 sensors have to be integrated and interconnected on an existing communication bus. The whole ribbon has stringent application constraints: Firstly, to correlate the pressure data to environmental pressure variations, the pressure offset compensation needs a time resolution better than 1ms. Secondly, to measure the pressure at the same time on the whole ribbon, channel synchronization delay smaller than 400µs is mandatory. Lastly, In order to be compliant with the existing infrastructure, the proposed microsystem must be able to provide a digital output in a frequency range between 200Hz and 1kHz.

An integrated-specific sensor interface was developed to compute a 16-bit, temperature-compensated pressure measurement. The challenges in this work were: compliancy with drastic packaging constraints, high resolution computation data in a low power budget, and innovative data buffering solution, compatible with the fully asynchronous and delay-constrained interrogation protocol. To optimize the overall power budget and leverage the analog processing, a first 150Hz low-pass filtering stage was realized at mechanical level using the packaging cavity. In regards to signal bandwidth (BW) and targeted Signal to

Noise Ratio (SNR), a switched caps sigma-delta converter is the best solution choice. For a 100Hz bandwidth, a secondorder modulator and a 512 oversampling ratio gives a 16 bits resolution. Using a digital channel filtering composed of a Sinc3 (1536 coefficients) and two half band filters (15 and 51 coefficients), the computation latency would have been higher than 150ms with the modulator clock. We thus proposed to use an innovative sliding window Finite Impulse Response (FIR) filter, triggered with the SPI BUS selection (CS) (Fig.1).

#### Figure 1 : Pressure sigma-delta architecture

For a 30Pa global precision, we had to compensate the thermal drift mainly due to the sensor (20Pa/°C) The 0.1°C temperature measurement resolution was performed using a 10bits resolution 10 Hz bandwidth sigma-delta converter (OSR=256). A size-optimized filter was designed, composed of a 94 coefficient Sinc3 with a decimator factor of 32, followed by a 16 coefficients Sinc2 decimated by 8.

Figure 2 : System on thin ribbon

The circuits were fabricated in 0.35µm CMOS technology. The measured pressure precision is 15 bits and 10 bits for temperature precision, for a sampling frequency between 200Hz and 1kHz and a power consumption of 9.2mW (including bus driving). The global system noise is limited to 24 Pa in a range of [20kPa/95kPa] and [-30°C/+60°C]. The whole ribbon answers at request with less than 1µs maximum delay between channels and 5ms maximum overall latency.

Related Publications :

[1] Condemine, C.; Willemin, J.; Bouquet, S.; Robinet, S.; Robinet, A.; Jouanet, L.; Regis, G.; Compagnon, O. & Vitry, S. (2013), '128 nodes 4.5 mm pitch 15-bit pressure sensor ribbon"Proceedings of the ESSCIRC (ESSCIRC), 2013 Proceedings of the', 229-232.

# An Adaptive Output Impedance Gate Drive for Safer and More Efficient Control of Wide Bandgap Devices

Research Topics : Adaptive gate drive, diode-less, HF converter, dead-time loss

R. Grezaud, F. Ayel, N. Rouger (G2ELAB), J.-C. Crebier (G2ELAB)

ABSTRACT: An adaptive gate drive circuit has been fabricated in AMS 0.35µm CMOS process to provide a safer and more efficient control of Wide Bandgap Devices (WBD). The gate driver has an adaptive output impedance for optimal turn-on/off driving conditions and a gate side power transistor switching state detector. Its impedance can be precisely adjusted from 0.7 $\Omega$  to 12.5 $\Omega$  during transitions. In a 800 kHz switching frequency diode-less WBD-based synchronous buck converter, the proposed gate drive circuit demonstrates secure but drastic dead-time reduction with a peak performance gain of 20% compared to a fixed dead-time of 50ns.

Wide Bandgap Devices (WBD) like GaN HEMT or SiC JFET offer outstanding performances for high switching frequency, high power density and high temperature applications. WBD can be used into most of converters in place of conventional silicon transistors because they are functionally close; however they are structurally different.

These new devices require more attention on the gate side because of smaller turn-on energy and faster transition times. When current and voltage slew rates become too important destructive overvoltage and faulty turn-on are omnipresent. In such cases by increasing the gate drive impedance, slew rates are limited and the safe operating area is extended. Conversely when transition times are too slow (at low output load) extra switching loss can be reduced by setting the lowest impedance.

Some of WBD, do not have a built-in body diode. In the view of improving synchronous converters' operation a very short dead-time is definitely desired. Secure drastic dead-time reduction is reached by adapting output impedance to balance the impact of the operating point and the temperature on switching characteristics [2] and so maintain the same WBD transition times.

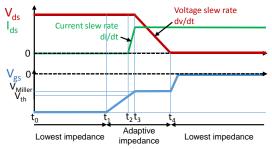

Figure 1 : Turn-on waveforms with adaptive output impedance gate drive  $% \left( {{{\mathcal{T}}_{{{\rm{s}}}}}} \right)$

The gate driver adapts its fall and rise output impedance between two switching periods and during steady states by respectively adjusting the number of parallel NMOSs and PMOSs constituting the output buffer. Moreover, a detection of the power device switching state has been implemented into the prebuffer, in order to ensure safest operations. When the gate to source voltage Vgs exceeds the Miller plateau voltage VMiller, the lowest impedance is automatically set as shown on Fig. 1. In such a way the output impedance selection is effective only during turn-on or turn-off and parasitic switching can be avoided.

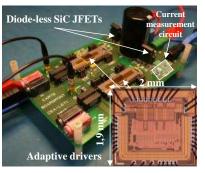

Figure 2 : 800kHz switching frequency diode-less vertical SiC JFETbased synchronous buck converter driven by the adaptive output impedance gate drive circuits

The adaptive output impedance gate drive circuit has been fabricated in AMS 0.35 $\mu$ m HV CMOS (Fig. 2). It can precisely control WBD with adaptive output impedance from 0.7 $\Omega$  to 12.5  $\Omega$  between two switching periods, by adjusting the impedance with an external control unit. Overvoltage due to parasitic inductances into a given synchronous converter has thus been reduced by 80%. Moreover in the diode-less WBD-based synchronous buck converter shown on Fig. 2, the proposed gate drive circuit demonstrates secure but drastic dead-time reduction with a peak performance gain of 20% compared to a fixed dead-time of 50ns.

Figure 3 : Turn-on of a SiC JFET driven by the adaptive gate drive circuit into the lowest and the highest output impedance mode: extend safe operating area but extra switching loss.

Related Publications :

<sup>[1]</sup> R. Grezaud, F. Ayel, N. Rouger, and J.-C. Crebier, "An Adaptive Output Impedance Gate Drive for Safer and More Efficient Control of Wide Bandgap Devices," IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Oct. 2013

<sup>[2]</sup> R. Grezaud, F. Ayel, N. Rouger, and J.-C. Crebier, "A Specific Characterization Method for Evaluation of Operating Point and Temperature Impacts on Wide Bandgap Devices," IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Oct. 2013

# A Self-Starting Fully Integrated Auto-Adaptive Converter for Battery-Less Thermal Energy Harvesting

**Research Topics : Thermal energy harvesting, adaptive charge pump, battery-less**

R. Grezaud, J. Willemin

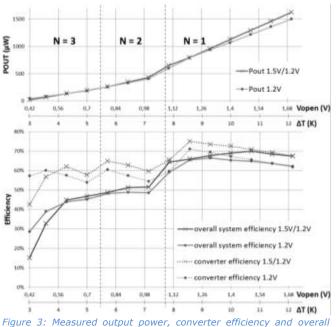

ABSTRACT: A fully integrated DC/DC converter capable of supplying energy to a battery-less sensor by extracting power from thermoelectric generators (TEGs) over a wide temperature gradient range (3K to 12K) has been fabricated in UMC180nm process. The power management unit of the converter enables to directly power a sensor with a 1.2V regulated voltage output. Under a special operating mode it can also manage larger power consumption operations during a short time. It starts converting at 250mV input voltage and provides up to 1.6mW output power with a 70% peak efficiency using a very low silicon area of 2.86mm<sup>2</sup>.

The power supply of wireless sensors is usually a primary battery which limits the deployment and the life time of the sensor. To reach energy autonomy in environmentally friendly conditions, a battery-free and fully integrated converter optimizing the global power extraction with a variable conversion factor is targeted. Previous work on battery-less thermal energy harvesting report efficient converter, but are not fully integrated.

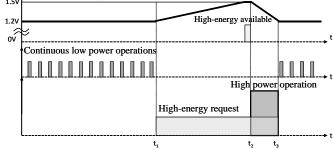

In [1] we propose a direct path between the scavenger and the application through an efficient converter. Such configuration improves the overall node efficiency [2]. As the wireless sensor is directly powered by the converter, the output voltage has to be regulated to assure stable performance. In the first converter operating mode, the output regulated voltage is set to 1.2V (until t1 on Fig. 1), providing smooth power supply for low power sensing operations. Thr converter can also power the node for a high consuming task (wireless communication) by using a special 1.5V mode. In this second mode, the harvested energy is accumulated in the output capacitor at higher voltage (until t3 on Fig. 1).

Output voltage V<sub>out</sub>

Related Publications :

Figure 1 : The Power management unit adapts converter operations according to the available input power and sensor node tasks

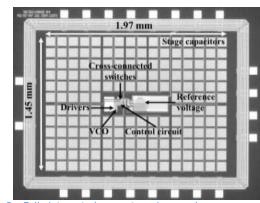

The converter was fabricated in UMC180nm process using 2.86mm<sup>2</sup> silicon area (Fig. 2). It is based on a crossconnected Dickson charge pump. By monitoring the available input power, the very low power control circuit adapts the number N of pumping stages to improve the overall efficiency (Fig. 3). The circuit is self-starting when the TEG output voltage is only 250mV. From a 3K to 12K thermal gradient, it provides from 22 $\mu$ W to 1,6mW output power with 70% peak overall efficiency (Fig. 3).

Figure 2 : Fully integrated converter micrograph

[1] R. Grezaud, J. Willemin, " A Self-Starting Fully Integrated Auto-Adaptive Converter for Battery-Less Thermal Energy Harvesting," IEEE New Circuits and Systems Conference (NEWCAS), June 2013.

[2] J.-F. Christmann, E. Beigne, C. Condemine, P. Vivet, J. Willemin, N. Leblond, and C. Piguet, "Bringing Robustness and Power Efficiency to Autonomous Energy-Harvesting Microsystems," IEEE Design Test of Computers, vol. 28, no. 5, pp. 84–94, Oct. 2011.

# HarvWSNET - A Co-Simulation Platform for Energy Harvesting Wireless Sensor Networks

#### **Research topics : WSN Simulation, Energy Harvesting**

A. Didioui, G. Vaumourin, V. Tran, F. Broekaert (Thalès Com), C. Bernier, O. Sentieys (INRIA)

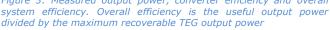

ABSTRACT: These papers [1,2] present the HarvWSNET co-simulation framework developed within the GRECO (GREen Communicating Objects) project. GRECO is a French ANR (National Research Agency) project whose aim is to design an energy efficient wireless platform that is totally autonomous thanks to energy harvesting (EH) capabilities and adaptive power management. The detailed modeling capability of HarvWSNET is illustrated by pre-prototyping a complex wind energy harvesting application for a peer-to-peer subway tunnel wireless sensor network (WSN) application.

The idea of extending WSN node lifetime by equipping each node with an energy harvesting (EH) subsystem has recently attracted a great deal of attention. Indeed, energy harvesting appears to be an ideal candidate for powering WSN nodes: the energy density available in the environment, whether solar, wind, vibrational or thermal in nature, is often compatible with the needs of a WSN application. While energy harvesting appears to be an extremely promising technology for extending WSN lifetime, new tools are required for accelerating time-to-market for these new systems. Indeed, in addition to validating the hardware and software components required by an application, pre-deployment studies must also validate the time-varying availability of the power source in the given application environment.

Figure 1 : Illustration of Subway EH-WSN Application

To this end, the co-simulation platform presented in [1-2] allows for a complete modeling of complex EH-WSN applications thanks to the association of a discrete-events WSN simulator (WSNET) with an industry standard continuous-time simulator (Matlab). This framework is employed to pre-prototype a data-aggregating peer-to-peer WSN consisting of 184 nodes installed at regular intervals of a subway-line tunnel (Fig. 1). Each node is powered by a small wind-turbine which harvests the wind generated by each train passage.

To pre-prototype this application, an accurate model of the wind energy harvester was developed (Fig. 2), including the rectifier, DC/DC converters and supercapacitor. Other models were also defined including models for in-tunnel signal propagation (Fig. 1), train mobility, TDMA-based MAC protocol, data aggregation and acknowledgement, and node power consumption.

#### Figure 2 : Wind Energy Harvester Model

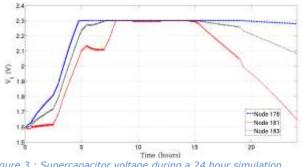

Simulation results show the time-varying behavior of each node's supercapacitor voltage (Fig. 3) which tends to recharge when train passage frequency is high and tends to discharge during the last 5 hours of the simulation when trains are at a stop. These simulations are used to evaluate the viability of this application, identify appropriate network architecture and determine sensor activity period, data delay and network autonomy in case of train traffic interruption. In addition, the importance of network and node-level power-aware protocols is illustrated since the network must adapt to the time-varying nature of the power source. Finally, the simulations reach a quick verdict as to the viability of this application, hence limiting the prototyping costs and delay and minimizing the time-tomarket of novel EH-WSN scenarios.

#### Figure 3 : Supercapacitor voltage during a 24 hour simulation

#### **Related Publications**

[1] A. Didioui, C. Bernier, D. Morche, O. Sentieys, "HarvWSNet: A co-simulation framework for energy harvesting wireless sensor networks", 2013 International Computing, Networking and Communications Conference (ICNC). [2] F. Broekaert, A. Didioui, C. Bernier, O. Sentieys, "Prototyping an Energy Harvesting Wireless Sensor Network Application Using HarvWSNet", ARCS 2013.

# Ultra Wide Band : Ultra-Fine and Robust Localization with Quadrature Receivers

#### **Research topics : UWB, Localization, Beamforming, Antennas**

D. Morche, G. Masson, S. De Rivaz, F. Dehmas S. Paquelet, A. Bisiaux (Mitsubishi), Fourquin, Gaubert, Bourdel (IM2NP)

ABSTRACT: In this project, we have demonstrated that high localization precision can be obtained using quadrature receivers. The down-conversion to baseband is exploited to filter out any unwanted signal. By combining RF filter, 5th order gm-CT filter, window integration and coherent integration, rejection higher than 80 dB can be achieved. Then the correlation with an orthogonal basis is exploited to reach very good ranging precision (few cms). Phase information can be used to improve even more the precision (few mms)

Localization technologies are facing a growing interest in the industry since they can offer a wide variety of applications. Among the different technologies, UWB is known to potentially offer the best precision. Whereas However, up the now, the performances of the existing solution were limited in terms of performances.

At the very beginning of UWB, most of the IR-UWB localization solutions were based on non-coherent receiver with poor performances. Since almost ten years, the interest in coherent architectures has been growing in order to reach better performances with improved robustness to out-of band blocker which is one of the main issues in Ultra Wide Band due to spectrum saturation.

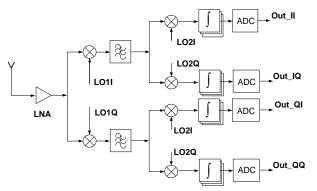

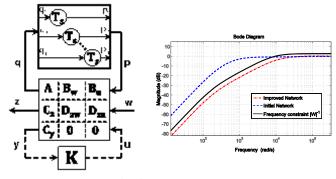

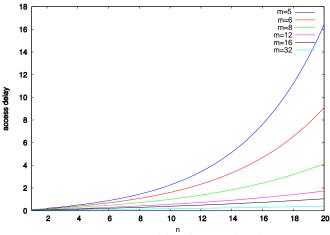

In this project [1], we have targeted low power, long range and high robustness localization applications. For that purpose we have selected a double quadrature receiver architecture which is presented in Figure 1 (without the frequency synthesis). This architecture enable us to use a low rate sampling frequency while keeping very good precision in the time of arrival precision. The second oscillator frequency is chosen to be a sub-multiple of the first one to simplify the PLL design.

Figure 1 : LORELEI Receiver Architecture

To reach high precision performances and long range, a 1.5 GHz bandwidth has been adopted. However, the receiver architecture is compatible with classical 500 MHz channel bandwidth. It can even switch from one channel to another without modifying the PLL frequency.

Then a classical gmC filter has been design to attenuate out of band signals by 20 dB using the well-known Nauta Cell. Following this filter, the signal is integrated during a dedicated window with a switched capacitor infrastructure. Lastly, the signal is converted from analog to the digital domain with a low power flash ADC. The whole circuit has been design using 130nm CMOS technology from STMicroelectronics.

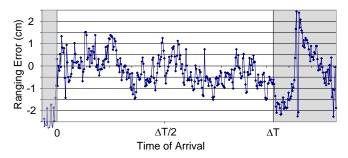

New metrics have been developed to extract the time of arrival of the received pulse. The ranging error is now lower than 1.5 cm as presented in Figure 2. Much better precision can be obtained by exploiting the phase information of the received signal. In that case, error is lower than 2,5mm but the precision becomes dependent of the antenna characteristics.

Figure 2 : Ranging error of the Time of Arrival Estimation as a function of the arrival time in the window

The obtained sensitivity is better than -95 dBm@1Mb/s justifying the architecture choice [2]. The 50mW power consumption is fully compatible with mobile devices. The proposed solution provides the lowest sensitivity and the best ranging precision. Since the architecture is fully coherent, the range (300m) can be extended even more by resorting to multi-antenna architectures. The performances of the localisation can be even more improved by extracting the angle of arrival of each path which has been shown to be possible with the proposed architecture [3].

This development paves the way for the industrialization of UWB localisation solutions.

Related Publications:

<sup>[1]</sup> D.Morche, G.Masson, S.De Rivaz, F. Dehmas S.Paquelet, A.Bisiaux, O.Fourquin, J.Gaubert, S.Bourdel "A Double Quadrature UWB Receiver for wide Range Localization Applications with sub-cm Ranging Precision" IEEE Journal of Solid-State Circuits 2013, Volume 49, Issue 10, October 2013

<sup>[2]</sup> D.Morche, M.Pelissier, G.Masson, P.Vincent "UWB : Innovative Architectures Enable Disruptive Low Power Wireless Applications » Invited paper in DATE Conference 2012

<sup>[3]</sup> Farid Bautista, Dominique Morche, Serge Bories, Gilles .Masson "Antenna Characteristics and Ranging Robustness with Double Quadrature Receiver and UWB Impulse Radio" ICUWB 2012

# A low power 60-GHz 2.2-Gbps UWB transceiver with integrated antennas for short range communications

#### **Research topics : mmW, UWB, CMOS, integrated antenna, wireless**

A. Siligaris, F. Chaix, M. Pelissier, V. Puyal, J. Zevallos, L. Dussopt, and P. Vincent

ABSTRACT: A 60-GHz low power fully integrated transceiver including antennas, fabricated in CMOS 65nm SOI and packaged in low cost QFN is presented. The circuit achieves 2 Gbps and 500 Mbps rates at 7.5 cm and 22.5 cm transmission ranges respectively. The transceiver energy efficiency is lower than 50 pJ/bit thanks to scalable power consumption using pulse generator and Super Regenerator Oscillator architecture.

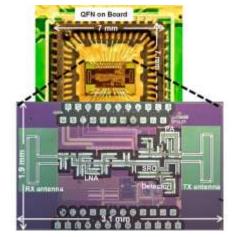

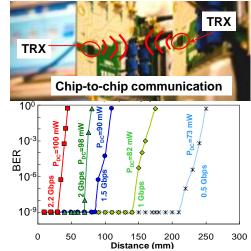

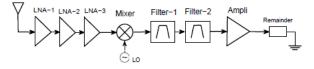

Future consumer mobile platforms need high rate wireless connections for data exchange and video streaming. 60-GHz band has been intensively explored for such purpose, but existing solutions exhibit high power consumption. This work describes a fully integrated 60 GHz low power transceiver, including the antennas, fabricated in a CMOS 65nm SOI technology. The chip is packaged in a low cost QFN pre-molded cavity. The circuit targets mobile devices requiring multi-Gbps wireless data transfer for pear-to-pear exchange, data synchronization and kiosk application. It can also be used in chip-to-chip or board-to-board wireless communications where low power consumption is required. Thanks to low complexity in the transceiver architecture and by using On-Off-Keying (OOK) modulation scheme, lower than 100 mW is attained for the whole communication at 2 Gbps throughput.

The transmitter is based in a switched pulse-injected oscillator. The input digital data to be transmitted are injected serially in the oscillator and a pulsed sine signal with center frequency at 61 GHz is generated. The pulse is next amplified by a single stage power amplifier and radiated by the integrated antenna. At the receiver side, the system uses a Super Regenerator Oscillator (SRO). It offers many advantages for wideband pulsed oscillating signals in terms of duty cycling capability, sensitivity bandwidth, and instantaneous gain. Synchronization of the SRO is performed with integrated DLLs. Finally an envelope detector and a comparator are used to decide if a "1" or a "0" is detected. Integrated antenna design takes into account the global chip environment like wire bonds, circuit and packaging metallic elements as well as the polymer material properties.

Wireless links are tested with two boards containing fully integrated transceivers placed in an office like environment (figure 2). For a BER  $\leq$  10-5, a 7.5 cm distance is achieved for 2 Gbps rate and up to 22.5 cm distance for 500 Mbps. This work shows an excellent trade-off between wireless transmission range, data rate and power consumption achieving better than 50 pJ/bit total energy efficiency, which is the best to our knowledge and sets the state-of-the art for this type of transceivers. The proposed circuit provides a fully integrated and low-cost solution for high data rate, low power, and short range wireless data exchange chipsets.

Figure 1 : Chip-in-package photograph (open lid) and details of the chip. Dimensions:  $3.1 \times 1.9 \text{ mm}^2$ .

Figure 2 : Experimental setup for wireless link and BER versus communication range for various data rates indicating the total transceiver dissipated power for each case

Related Publications:

A. Siligaris, F. Chaix, M. Pelissier, V. Puyal, J. Zevallos, L. Dussopt, and P. Vincent, "A low power 60-GHz 2.2-Gbps UWB transceiver with integrated antennas for short range communications," IEEE Radio Frequency Integrated Circuits Symposium, pp. 297-300, June 2013.

J. Zevallos Luna, L. Dussopt, and A. Siligaris, "Hybrid On-Chip/In-Package Integrated Antennas for Millimeter-Wave Short-Range Communications," Transactions on IEEE Antennas and Propagation, vol. 61, no. 11, pp. 5377-5384, Nov. 2013.

L. Dussopt, J. Zevallos Luna, and A. Siligaris, "On-chip/in-package integrated antenna for millimeter-wave medium and long-range applications" International Workshop on Antenna Technology, (iWAT), pp. 203-206, March 2013.

# Inductor shielding strategies to protect mmW LC-VCOs from highfrequency substrate noise

#### Research topics : CMOS RF integrated circuits, temperature sensor, testing, self-healing

J.L. González, M. Molina (UPC), X. Aragonés (UPC) D. Mateo (UPC)

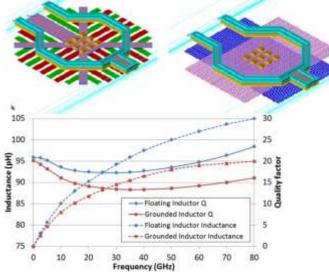

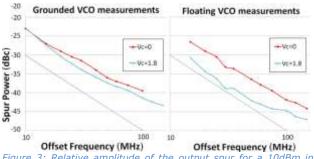

ABSTRACT: High frequency signals coupling through the substrate is the main source of VCO pulling in fully integrated transceivers [1]. In this work we investigate and compare two shielding strategies commonly used to avoid this effect: grounded shields and floating shields. The results of our investigations show that, even if the coupling from the substrate is very similar in the two cases, the final effect on the VCO is strongly reduced by the floating shield inductor due to its larger quality factor which reduces the ability of the coupled interferences to pull the oscillator.

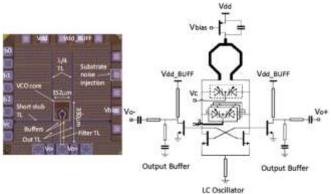

The use of grounded shields (GS) under integrated inductors is a common practice today. It allows to provide a controlled environment to the inductor and to reduce the coupling of undesired signals from the substrate. We show, however, that using a floating shield (FS) is an even better idea regarding the resilience of the VCO to interference signals coming from the substrate [2]. Both types of inductors are illustrated in Fig. 1. The inductors where sized for a 60 GHz VCO [3] shown in Fig. 2. The prototype IC includes a pad contacting to the substrate through a large line of p+ contacts all along the right edge of the circuit (see Fig. 2). This pad is used to inject an interference signal into the substrate at a frequency close to the oscillator frequency. The power of the signal and its offset with respect to the VCO oscillator is set so that no pulling is observed. This allows measuring the spur appearing at the output of the VCO using a signal analyzer.

Figure 1: Integrated inductor with grounded (left) and floating (right) shield, and comparison of quality factors and inductance value.

First of all, we have done 3D EM circuit simulations and we have found that the coupling from the substrate to both inductors is very similar.

Figure 2: 60 Ghz VCO using either type of inductor.

Secondly, an experimental analysis of substrate interference onto the VCO has been done [2]. The measurements results are shown in Fig. 3. Two extreme values of control voltage Vc where used, which correspond to the extreme values of quality factor for the tank using either of the inductors (GS:7.1-9.7, FS:8-11). The "grounded" shield inductor shows large spur amplitudes compared to the floating shield inductor for the high Vc value, which corresponds to the case where the overall tank quality factor is dominated by the inductor. For lower Vc values, the varactor quality factor, which is the same in both cases, plays a more important role. Therefore we can conclude that the higher quality factor of the FS inductor VCO is the reason of its better resilience to substrate coupled interference.

Figure 3: Relative amplitude of the output spur for a 10dBm input tone at the substrate as a function between the VCO and the substrate signal frequency offset.

[1] M. Molina, D. Gómez, X. Aragonés, D. Mateo, J.L. González, "Design of a 2.5 GHz QVCO robust against high frequency substrate noise," Microwave and Optical Technology Letters, Vol. 53, No. 7, pp. 1632–1637, July 2011.

[2] Marc Molina, Xavier Aragonés, Diego Mateo, José Luis González, "Inductor shielding strategies to protect mmW LC-VCOs from high [3] J.L. Gonzalez, F. Badets, B. Martineau, D. Belot, "A 56-GHz LC-Tank VCO With 17% tuning range in 65-nm bulk CMOS for wireless

HDMI, "IEEE Transactions on Microwave Theory and Techniques, Vol. 58, No. 5, pp. 1359-1366, May 2010.

**Related Publications:**

## A 285 GHz sub-harmonic injection locked oscillator in 65nm CMOS

#### Research topics : mmW, sub-THz, VCO, CMOS, locking

J.M. Guerra, A. Siligaris, J.-F. Lampin (IEMN), F. Danneville (IEMN), P. Vincent

ABSTRACT: 285 GHz Sub Harmonic Injection Locked Oscillator (SHILO) is presented using a standard 65nm CMOS process. The architecture of this oscillator is based on the differential LC tank with push-push but adapted to obtain a third harmonic oscillation. The output power is -19 dBm at 285 GHz for a dc power of 70 mW. This oscillator offers a measured phase noise of -96.3 dBc/Hz at 10 MHz and -80.5 dBc/Hz at 1 MHz, and a tuning range from 284.2 GHz to 289 GHz. The SHILO can be locked all along the tuning range with an injection signal corresponding to one sixth of the output frequency. The chip size is 921x451  $\mu$ m<sup>2</sup>.

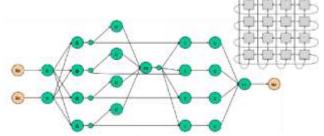

Sub-THz frequencies are explored for applications such as THz imaging and high throughput rate short-range wireless communications. This work aims to explore the feasibility of one of the most challenging blocks in such systems: the local oscillator. Indeed, designing oscillators operating close or at higher frequencies than the cut-off frequencies of the transistors needs new designing techniques. The common technique is sub-harmonic generation, which means that a fundamental tone is synthesized below the cut off frequency and higher harmonics are boosted using push-push, triplepush or quadruple-push techniques. Here, a modified version of the classic scheme of second harmonic generation is presented in order to exploit a third harmonic. Moreover, the designed and fabricated oscillator aims at its integration into complete frequency synthesizers. For that, a subharmonic injection signal is used in order to lock the oscillator and thus to generate a 285 GHz output signal that copies the reference signal frequency and phase noise.

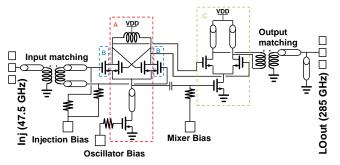

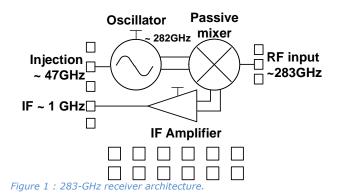

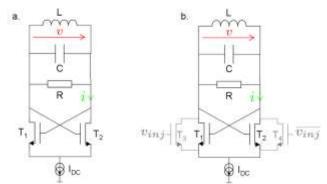

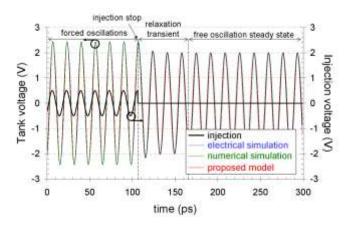

The architecture of the sub harmonic injection locked oscillator is presented in Figure 1. A differential oscillator generates the fundamental signal (part A); the second harmonic is obtained using a quarter wavelength transmission line (push-push technique). The injection transistors (part B) are used for locking the oscillator in order to stabilize the oscillation frequency and fix the phase noise on the injection source. The injection signal (around 47 GHz) is one sixth of the output oscillation frequency. The third harmonic is generated by a single balanced differential active mixer (part C) that mixes the fundamental tone and the second harmonic obtained by push-push (push-push & mix). Output 50 Ohm matching is adjusted to 285 GHz using microstrip transmission lines and an output balun for single ended measurements. Thus, lower frequencymixing products are rejected.

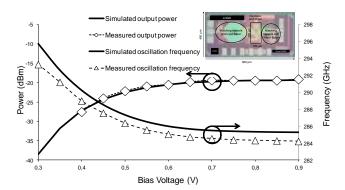

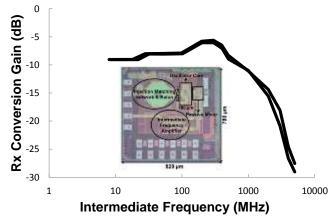

Measurements were carried out under probes. Figure 2 shows the free running oscillation frequency that spans from 284.2 GHz to 289 GHz while the output power varies from -19 dBm to -27 dBm. We observe that simulations fit measurements with good accuracy which validates the design methods and models.

Figure 1: 285-GHz oscillator architecture.

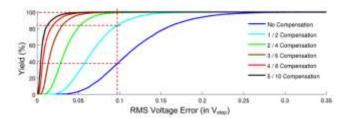

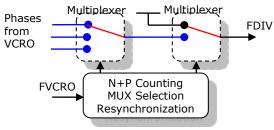

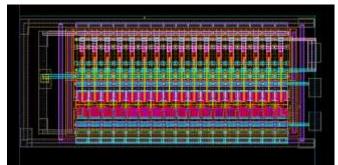

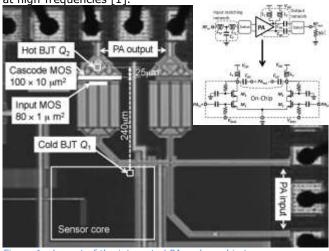

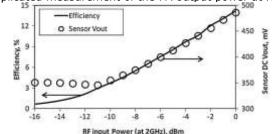

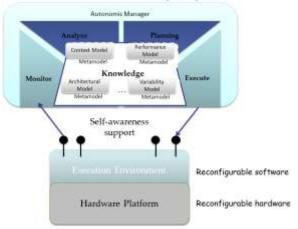

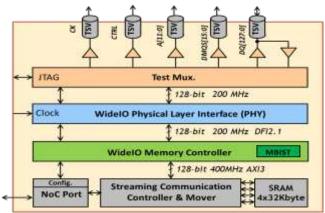

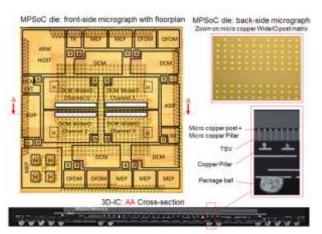

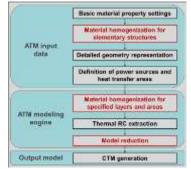

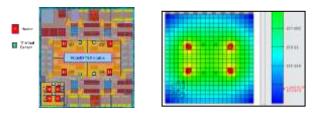

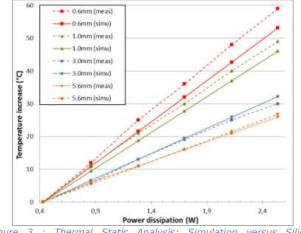

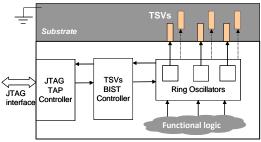

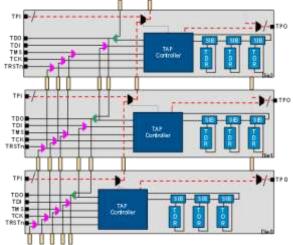

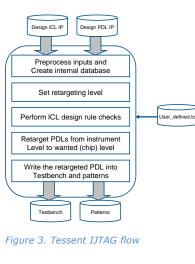

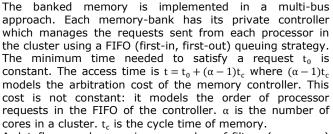

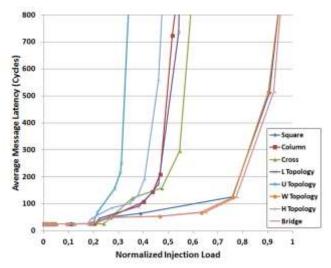

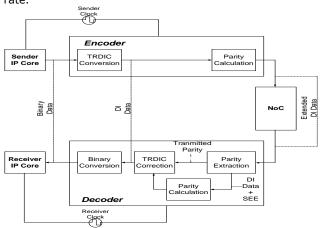

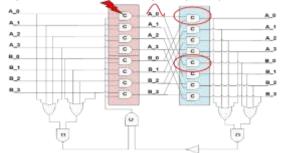

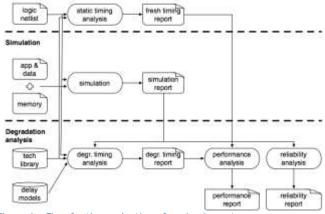

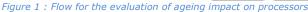

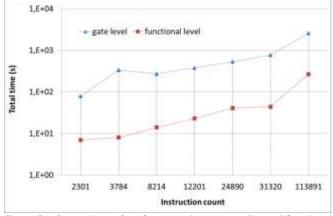

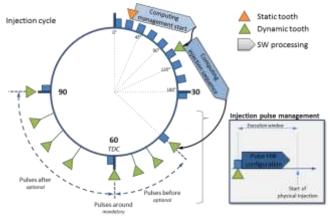

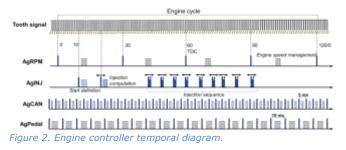

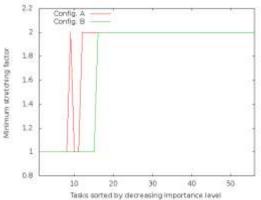

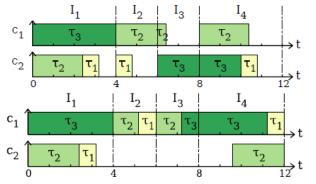

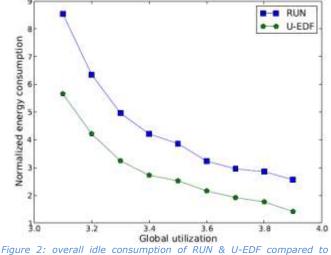

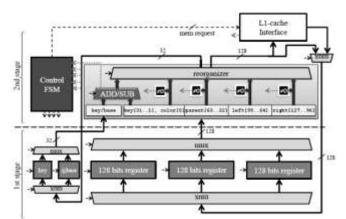

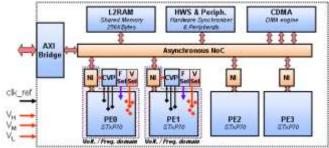

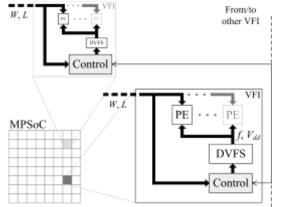

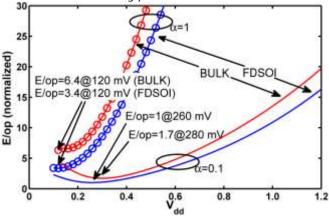

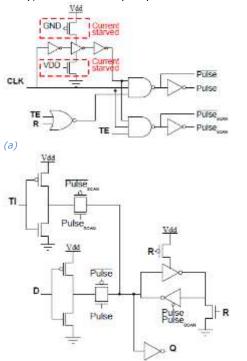

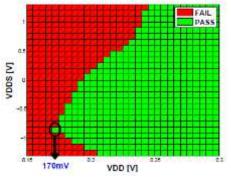

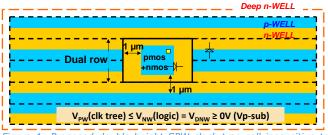

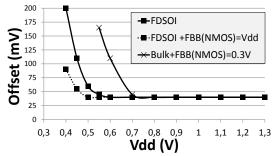

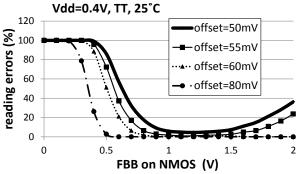

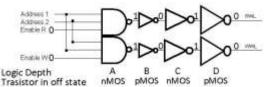

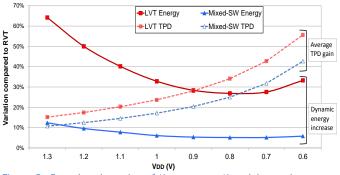

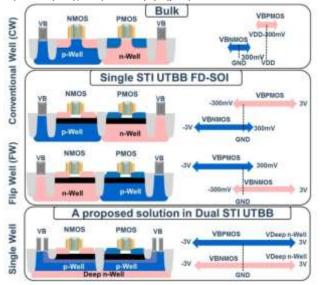

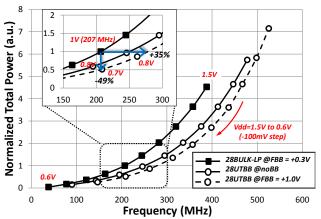

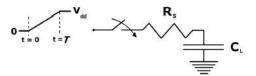

Figure 2: Output power and free running oscillation frequency vs. bias voltage. Symbols: measurements. Line: simulation. Inset: chip micrograph.